Altium Designer 是市场上应用广泛的印刷电路板设计解决方案。Altium Designer 超过35年的创新和发展,致力于创建一个真正统一的设计环境,使用户能够轻松连接到印刷电路板设计过程的各个方面。Altium Designer提供统一设计环境,使工程师能够使用单一视图全方位查看从原理图到PCB布局再到设计归档的整个PCB设计过程。在同一个地方访问所有设计工具,使工程师可以在相同的直观环境中完成整个设计过程,并快速交付高质量的产品。

最新更新

最新更新

1、在原理图上移动/拖动对象时,如果已放置了位图文件,则性能会受到明显影响。

2、交叉选择功能启用后,在原理图图纸上选择区域时会出现延迟,在选择较大区域时尤其如此。

3、在某些情况下,当标注元件时,会遇到“EOleException: Object reference not set to an instance of an object”错误。

4、在某些情况下,当进行确认时,会遇到“System.NullReferenceException: Object reference not set to an instance of an object”错误。

5、在某些情况下,会遇到Access Violation(地址为“AdvSch.dll”模块中的0000000149D1BE14)。

6、打开并置顶Properties面板后,在选择包含活动链接的说明或文本框时,会观察到明显的延迟。

1、显著提高了刚柔结合板设计中的整体布线性能。

2、恢复搁置的多边形铺铜(在Preferences中启用自动多边形重新铺铜选项)时,性能将大幅降低。

3、在定义与差分对布线规则一起使用的Impedance Profile时,添加了Common Mode Impedance(Zcomm),作为Simbeor计算得出的传输线数据的一部分。

4、对于特定PCB,并不总能检测到最小宽度违规。添加了PCB.Rules.Width.CopperLoopsCalculation选项,以改进铜环路段宽度的计算。

5、现在,当将折叠段连接到导线时,软件使用调整模式的Miter参数而非通用交互式布线Miter Ratio。

6、现在,PCB Layout Replication工具提供在检测到多个元件具有相似连接的目标块中手动映射元件的功能。

7、优化了渲染盲孔时的性能。

8、在启用‘Altium Light Gray’主题的情况下,当添加新用户材料或编辑现有材料入口时,Altium Material Library对话框中的文本难以辨认。

9、在Properties面板打开、置顶且其Health Check选项卡处于活动状态的情况下,当开始移动PCB文档上的任何对象时,会观察到明显的延迟。

10、Section View功能现已在此版本中正式公开。

11、EngineX功能(已增强Clearance Rule、Expression Engine和DRC执行)现已在此版本中正式公开,并默认启用以提高性能。

12、当使用Diff Pair Router(Any Angle)进行交互路布线时,如果缺少Diff Pair Routing规则,将会发生崩溃。

13、在Project Options中更改其参数值后,设计区中显示的已放置特殊字符串(使用TrueType字体)被截断。

14、当从BGA元件的焊盘进行交互布线并启用Width_BGA设计规则时,会观察到明显的延迟。

15、在焊盘和多边形铺铜位于同一网络中,且焊盘孔径>=铜皮尺寸的情况下,当启用PCB.Rules.HoleClearance选项时,软件会以错误的方式进行多边形铺铜(至焊盘边缘)。

16、在启用PCB.Text.TTFontSaving选项的情况下,关闭并重新打开PCB后,无法选择已放置的文本框(旋转360度并设置为使用TrueType字体)。

1、就比较结果而言,现在可以在PCB CoDesign面板的‘Other’类别下找到Via Stitching和Via Shielding入口。

2、在特定情况下,合并变更会导致“This implementation is not part of the Windows Platform FIPS validated cryptographic algorithms”异常。

1、对于Via Style规则,现在如果PCB端没有已定义的过孔模板(通过关联的Pad Via库),则过孔模板添加功能将被禁用。

2、在创建新项目且Constraint Management选项被启用的情况下,PCB编辑器的Design菜单中将不再显示‘Rule Wizard’入口。

3、现在,可以通过ECO流程将Physical和Electrical视图上定义的约束从PCB传输到Schematic。

4、现在,在Clearance矩阵中输入值时,会忽略孔间距。

5、在Constraint Manager的All Rules视图(从PCB访问时)上,单击已添加的Board Outline Clearance规则的单元值后,Altium Designer将“冻结”。

1、在Draftsman文档上改选不同类型对象以及取消选择(通过点击对象之外的位置)时,存在明显的滞后。

2、 现在,Bookmarks面板可与Harness Draftsman文档(.HarDwf)和Multi-board Draftsman文档(.MbDwf)搭配使用。

3、当使用调用由项目参数(嵌套参数)驱动的文档参数的特殊字符串时,特殊字符串不会被转换。

1、将ODB++数据导出到PCB文件时,不同层上相同x、y位置的盲孔被错误地导出为通孔。

1、导出时,File » Export菜单上的入口名称已从‘3D Layout’更改为‘3D-MID’。

1、添加了对从Wiring Diagram到Layout Drawing的多部件元件数据传输的支持。

2、已清理各种UI元素,以删除多个不适用于Harness Design的功能和控件。

3、通过新增在导线参数中定义原色/二次色/三次色和边框颜色的功能,添加了对多色(条纹)导线的支持。

4、现在,在Wiring Diagram中作为带连接的Shield的一部分定义的Shield Wire可以在Layout Drawing中的连接点终止。

5、现在,在Draftsman文档中定义Wiring List对象的属性时,Columns选项卡提供与BOM表类似的Move Left/Right按钮和一个Order列。

6、现在,在Draftsman文档中定义Connection Table对象的属性时,Columns选项卡提供与BOM表类似的Move Left/Right按钮和一个Order列。

7、在某些情况下,当在Wiring Diagram上拖动导线时,导线优化会因导线被拼接而失败,尤其是当导线连接到引脚并具有可见参数时。

8、创建涉及导线周围线缆/屏蔽对象的新线束布线元件时,在Harness Wiring编辑器中选中线缆/屏蔽对象时,导线不会高亮显示。

9、在Layout Drawing上,删除中间连接点后,线束不会自动合并。

10、使用Smart PDF从Wiring Diagram/Layout Drawing生成PDF时,文本框和说明中定义的任何位号标识符链接在单击时均不起作用。

11、仅生成Wiring Diagram的PDF时(使用Smart PDF Wizard),颜色模式选项仅可用于/适用于Additional PDF Settings页面上的Layout Drawing。

12、将元件放入Wiring Diagram后,在元件级别定义的线束布线元件(作为Workspace Library的一部分创建)参数不存在。

13、在Wiring Diagram上,Cable/Shield/Twist位号标识符的Duplicate Designator警告已被删除。现在,您可以使用相同位号标识符拆分对象并将其用于不用的位置。

14、如果绞线/屏蔽与Wiring Diagram上多个位置的导线相关联(使用相同位号标识符),则选择绞线/屏蔽实例将高亮显示组中的所有关联导线。

15、在Wiring Diagram上拼接现有导线并执行标注后,生成的导线未被标注。

16、现在,HarDwf文档支持同一项目中的多个Wiring Diagram文档,借助该功能,您能够选择从中生成(并更新)已放置视图的具体文档。

1、在某些情况下,会遇到Access Violation(地址为“X2.EXE”模块中的0000001400137E7A)。

2、多次更改了Altium Light Gray UI主题的颜色,从而帮助提高界面的对比度。

3、在某些情况下,在‘Your Business Email’字段中输入一定数量字符后,无法通过Altium Designer Installer进行SSO登录。

4、访问License Management页面时,如果存在S/N或Activation Code相同的许可证,则会发生异常。

1、若在MPS面板中预先选中了一个类别,浏览至某个元件(在Components和Explorer面板中)并使用Part Choices菜单在MPS面板中将其打开时,将无法找到该部件。

2、现在,连接到Enterprise Server(v6.0.5)时,服务器会在批处理模式下为Component编辑器(在Batch Editing模式下)中的所有选定元件生成Item ID。

3、Save to Server对话框不显示已在Altium Designer外部(通过Windows操作)删除的文件。

4、在Manufacturer Part Search面板以及可以访问Part Choices的所有位置添加了对SiliconExpert‘Product Change Notice’的支持。

5、提高了打开大型、多年设计项目时的VCS性能。

6、从Manufacturer Part Search面板下载特定元件( R7F7015813AFP-C#AA3)时(作为文件库),仅下载了其三个相关封装中的一个封装。

7、连接到“预置”Workspace后,当实际没有打开任何项目时,可以从Project菜单中使用‘Make Available on Server’命令。

8、 现在,默认在Manufacturer Part Search和显示Part Choices的所有位置显示“Free”SiliconExpert参数(Lifecycle、YTEOL和RoHS Status)。

9、现在,当比较两个选定部件时,Manufacturer Part Search面板的‘Selected Part Details’区域支持SiliconExpert参数。

10、当有多个数据提供商(Octopart、IHS Markit和SiliconExpert)时,作为Manufacturer Link添加的ActiveBOM解决方案新增了对汇总生命周期信息的支持。

11、元件面板UI改变。对于根节点,使用‘All’而非Workspace名称。当选中子类别时,完整类别路径中不再体现根节点。

12、 添加了在ActiveBOM中仅使用“Free”SiliconExpert参数(Lifecycle、YTEOL和RoHS Status)的功能。

13、从远程中央存储库打开基于Git的项目时,Commit命令已重新添加到右键单击History & Version Control上下文菜单中。 (BC:22629)

14、当本地项目文件夹中存在同名文档(不在VCS下)时,运行‘Update Whole Project’命令会导致“conflict prevents checkout”Git错误。

15、向BOM元件添加多个替代项时(包括已在其他位置添加的替代项),随后出现的Warning对话框会将用户引导至未被添加的其他有效选中替代项。

16、无法将相同替代部件添加到多个替代组中。

1、导入特定 Allegro设计文件时,导入的电源平面内有死铜。

2、现在,导入Xpedition库时,3D Body高度不同的封装的命名具有唯一性(基于高度)。封装的高度值来源于现有CSV文件。

3、对于之前(仅)导入原理图符号的Xpedition库,您现在可以选择将封装模型作为现有项目结构的一部分导入PCBLib。

1、当使用TF对特定设计运行OP分析时,生成的‘Transfer Function’图为空。

2、当针对特定设计运行带有Noise的AC分析时,生成的‘Noise Spectral Density’图和‘Integrated Noise’图为空。

3、通过Sim Model对话框将该模型分配给原理图元件时,无法识别为库/Workspace内仿真模型定义的应力模型(和参数)。

4、通过Sim Model对话框将库/Workspace内仿真模型(无定义应力模型)分配给原理图元件时,无法保存‘Unknown’应力模型类型。

产品特点

产品特点

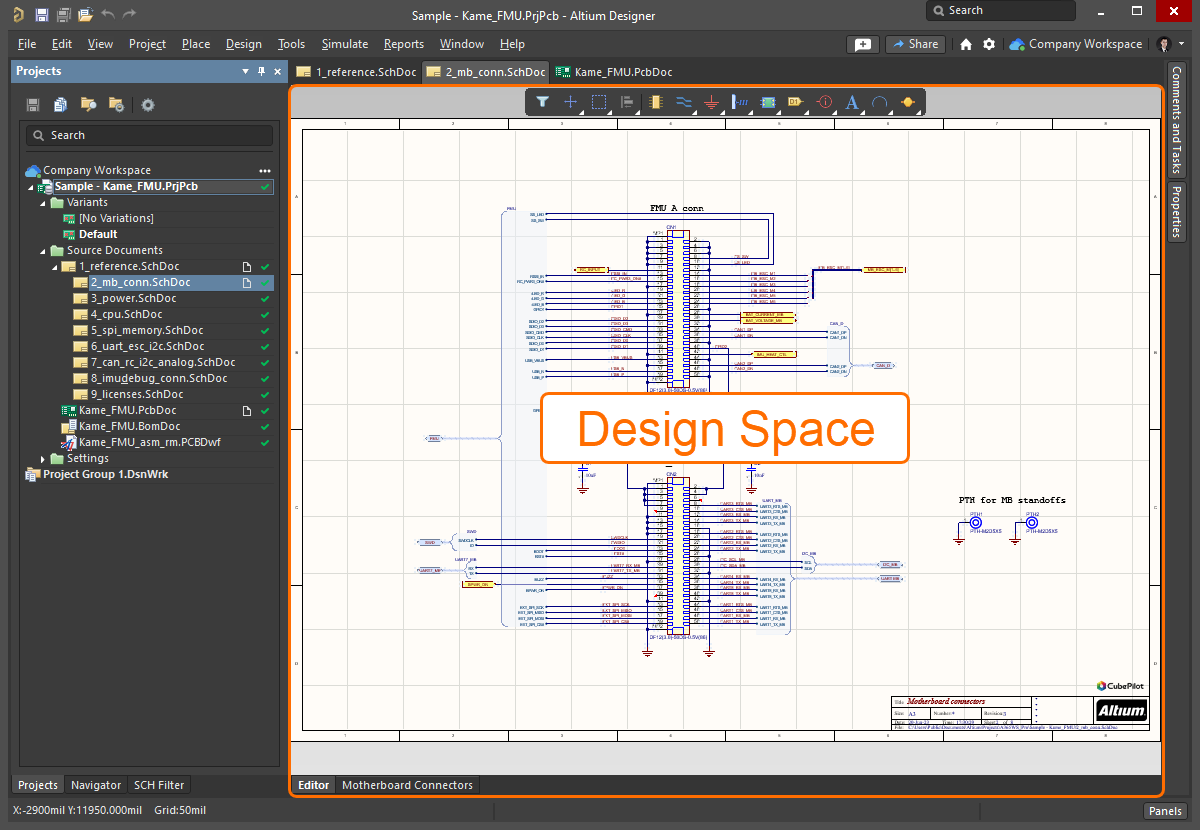

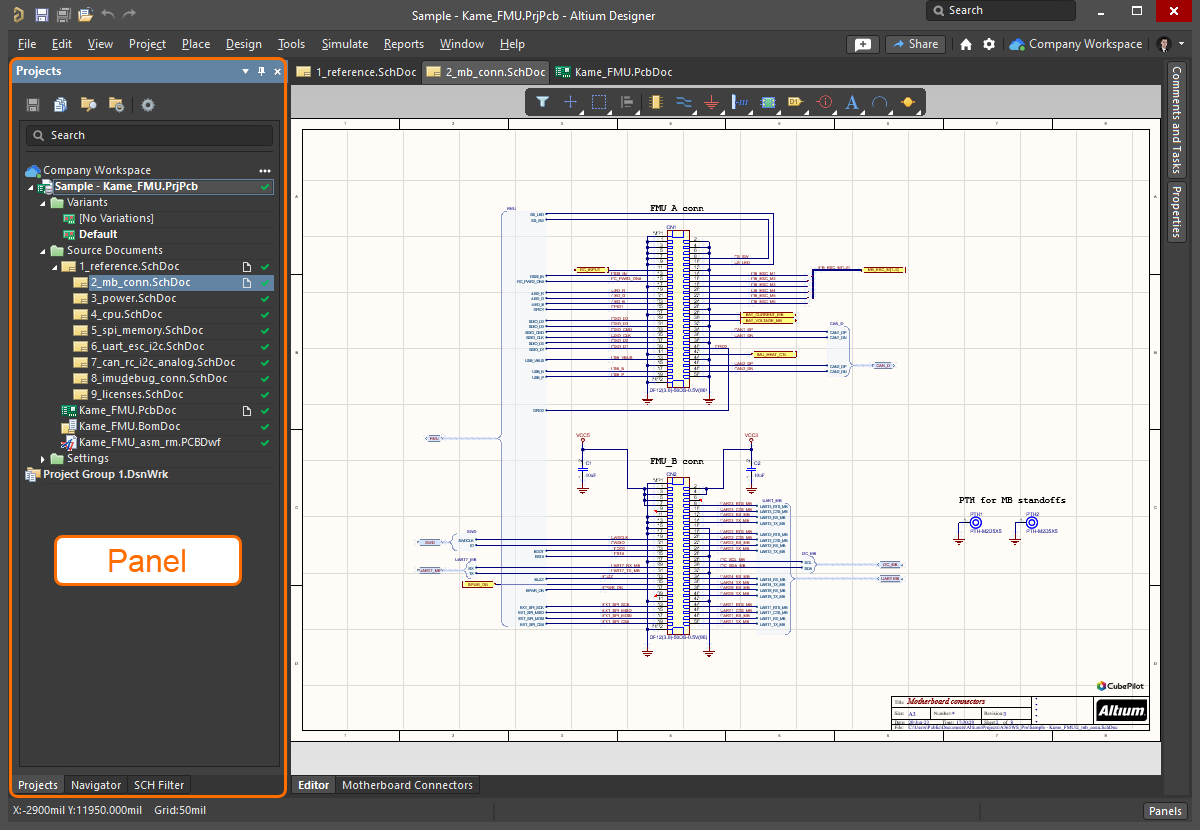

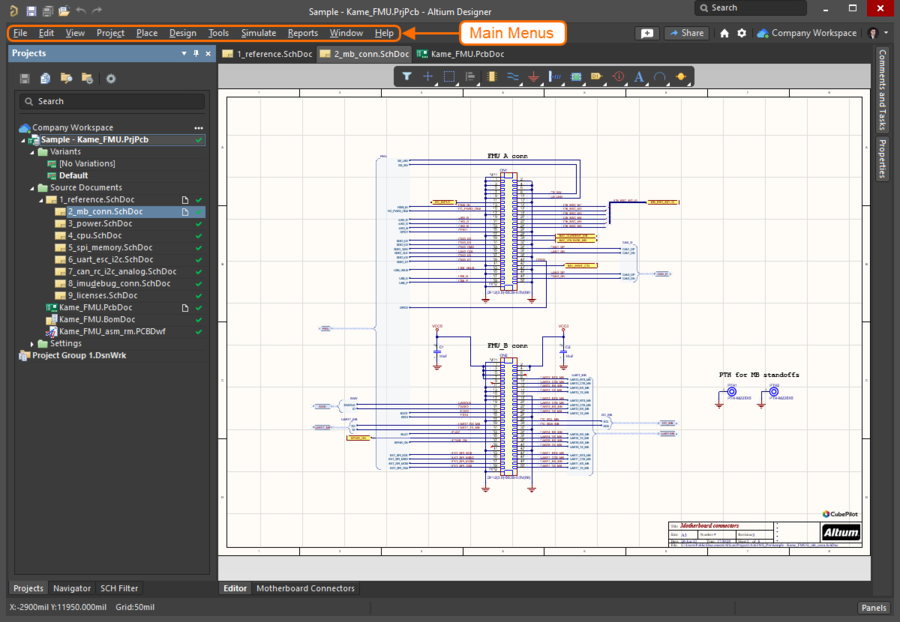

1、统一的设计体验

直观的用户界面让创建PCB设计变得毫不费力,从设计构思到制造,为您连接电子设计过程中的每一个细节。

2、统一的数据模型

编译项目以创建一个内聚模型,该模型可作为设计过程的核心。从这个中央模型可轻松地访问和操作模型中的详细数据(原理图、布局、仿真),而无需为每个设计元素单独存储数据。

3、ECAD/MCAD无缝集成

每次设计变更均可在Altium Designer和SOLIDWORKS®、PTC Creo® Parametric™、Autodesk Inventor®或Autodesk Fusion 360®之间保持同步。允许ECAD和MCAD设计人员在熟悉环境中工作,且无需进行繁琐的文件交换或手动转换。

功能配置

功能配置

Altium Designer共有3个功能配置包:标准版, 专业版, 企业版

注:以上功能配置信息仅供参考,实际功能配置信息以真实软件为准,解释权归软件制造商所有。

系统与硬件要求

系统与硬件要求

| 项目 | 最低配置 |

|---|---|

| 操作系统 |

Windows 10(仅64位) Windows 8.1(仅64位) |

| CPU | 英特尔®酷睿™i5处理器或同等处理器 |

| 内存 | 4GB RAM |

| 存储 | 10GB硬盘空间(安装+用户文件) |

| 显卡 | GeForce 200系列 / Radeon HD 5000系列 / Intel HD 4600 |

| 显示器 |

1680x1050(宽屏)分辨率的显示器 1600x1200(4 : 3)分辨率的显示器 |

| 其他 |

- |

产品说明

产品说明

Altium Designer支持:

- 原理图设计系统(SCH):主要包括原理图编辑器和 原理图模型库编辑器两部分。功能主要是绘制电路原理图,并为以后的PCB设计做准备

- 印制电路板设计系统(PCB):主要包括PCB图编辑器和 封装模型库编辑器两部分功能主要是绘制PCB图,及生产印制电路板的各种文件

- FPGA设计系统:功能主要是进行可编程逻辑器件的设计,并将设计完成后生成的熔丝文件下载到可编程逻辑器件中,以制作具备特定功能的元器件

- VHDL设计系统:功能主要是利用硬件编程语言(VHDL)设计集成电路(IC)

核心功能:

管理库:

Altium Designer提供完整的器件库管理方法,可快速、便捷、灵活地搜索器件,并自动生成设计库文件报告。其具体内容有:

- 包含原理图元件符号与PCB封装器件的集成库

- 可智能创建原理图符号库和PCB封装库

- 查找供应商器件库

- IPC标准封装向导

- 完全数据库驱动的器件信息系统数据库(DBLib)

- 版本可控的元件库

原理图设计:

- 可导入其他版本的设计项目

- 多样化工程管理模式

- 原理图环境中的PCB规则定义

- 高亮显示联通网络

- 强大的全局编辑功能

- 在工程中链接相关文档

- 可传输数据的智能粘贴

- 多种文件格式输出

- 材料清单BOM输出

- 开放总线OpenBus系统

- 版本控制

- 原理图层次化设计。

PCB设计:

- 差分对布线

- 蛇形走线功能

- 交互式长度调整

原理图设计:

- 总线布线

- 智能走线

- 支持BGA逃逸式布线

- 推挤功能及绕线引擎

- PCB走线切割和智能拖曳

- 自定义交互式布线

- 阻抗布线功能

- 图形硬件加速器(DirectX)

- 增强敷铜管理系统

- 敷铜多边形放置和编辑

- 器件重新装配

- 图元文件粘贴

- 显示动态网络

- 支持TrueType字体

- 反转文本

- 槽形和方形焊孔

- PCB翻转布局布线

- 提供Board Insight TM洞察功能

- PCB放大镜功能

- 增强的PCB设计规则检查

- 自动布线支持

- PCB中拼板功能

信号仿真与分析:

- 新增SIMetrix/SIMPLIS仿真引擎

- 仿真分析

- 支持PSPICE仿真模型

- 确保高速信号的完整性分析。

FPGA设计:

- 跨平台的FPGA设计

- 虚拟仪器实时交互式调试

- 边界扫描Live交互式调试

- 图形化的系统控制功能

- 混合HDL和原理图输入

- 嵌入式软硬件系统协同设计

- 在物理层调试JTAG器件

- 新增FPGA外设核

CAM输出制造:

- 支持274X格式的Gerber文件输出及查看

- 支持Gerber文件的编辑修改

- 支持DFM设计

- 支持CAM文件转换PCB文件

软件优势:

系统特征:

- 在统一的用户界面中可以使用全部软件

- 集成了电子产品开发的全部技术和能力,在开发的各个阶段不需其他应用软件

- 高度定制化的设计环境,包括全部工作界面和自动生成通用任务的智能脚本系统

- 提供可视化文件管理、备份、版本控制和不同版本之间比较

- 集成了版本控制系统,可进行版本控制和文档变更管理

- 提供全局查找和编辑功能

- 强大的在线文档搜索功能,可提供动态帮助

- 提供多显示器支持功能

- 在原理图和PCB间提供强大的综合功能,可控制变动且可视化

元件库:

- 集成化的元件库包含全部模块信息,如符号、封装、电路仿真和信号分析模型

- 数据库中保存全部元件,可直接从数据库中查找和放置元件

- 多种格式文件输出。

信号完整性分析:

- 布线前后的信号完整性分析

- 信号集成可作为规则检测的一部分,更容易发现错误。

电路仿真:

- 支持Spice 3f5、XSpice、PSpice仿真,支持仿真阵列。

设计图输入:

- Altium Designer允许与其他任何应用软件互相拷贝有效资源

- 智能粘贴可在拷贝和粘贴过程中传输数据

- 布线过程具有优化功能

- 强大的询问引擎提供了多对象的筛选、隐藏和编辑功能

功能:

性价比:

易用性:

-

Altium Designer对数据库使用 Excel 工作表时是否有限制?

-

altium designer怎么设置中文?

-

Altium designer10器件删了怎么找回

-

altium designer晶体管在哪?

回答的内容不能为空

还能输入100个字符 -

Altium Designer 里面如何找想要的元件啊?

回答的内容不能为空

还能输入100个字符

苏公网安备 32059002002276号

苏公网安备 32059002002276号

功能:

性价比:

易用性: