Synopsys VCS是Synopsys公司旗下的一款业界领先的仿真器,支持本征断言(native assertion)描述、自动测试平台生成技术(testbench)、以及代码和断言覆盖引擎,确保智能化验证的实现。

VCS 数字逻辑仿真器和VCS MX混合HDL语言仿真器都是Synopsys的智能RTL验证解决方案的基石。VCS中本征代码支持 (Native)技术确保了设计验证的效率、性能和质量,并缩短了验证周期。VCS中的本征代码技术实现了在单一工具中,支持可验证性设计(DFV),及 覆盖率驱动和约束的随机激励生成。其本征对断言的支持和所包含的丰富的断言检查工具库保证了设计人员能够方便地采用DFV技术来查找错误和提高验证质量。 此外,断言可以作为设计要求重复利用,在Synopsys的混合RTL规则验证产品Magellan中进行形式验证。VCS对专用集成电路(ASIC)生产商的建模和仿真签核(Sign-off)提供了支持。

VCS对统一的设计和验证语言标准SystemVerilog提供支持。SystemVerilog增强了设计人员的能力,加快了验证速度并提高了验证的质量。对于要求在RTL环境中使用SystemC模型进行验证的设计团队,VCS提供了支持OSCI SystemC的直接内核接口(DKI)和支持System Studio的直接内核接口(DKI)。

Synopsys VCS

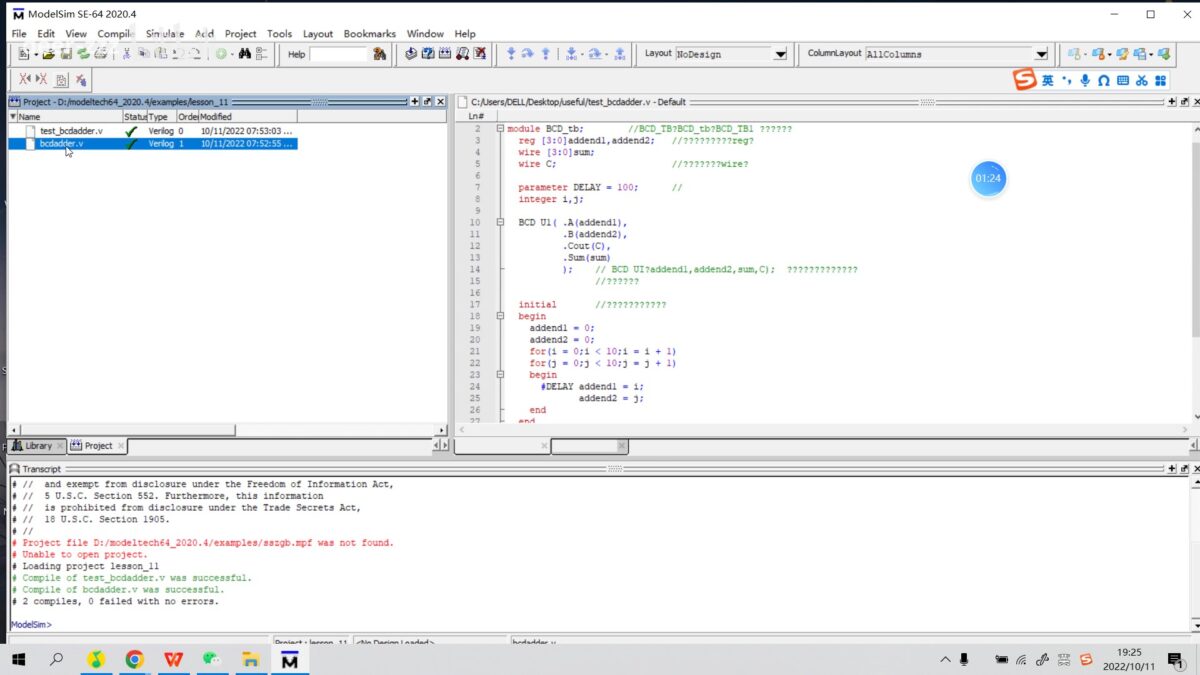

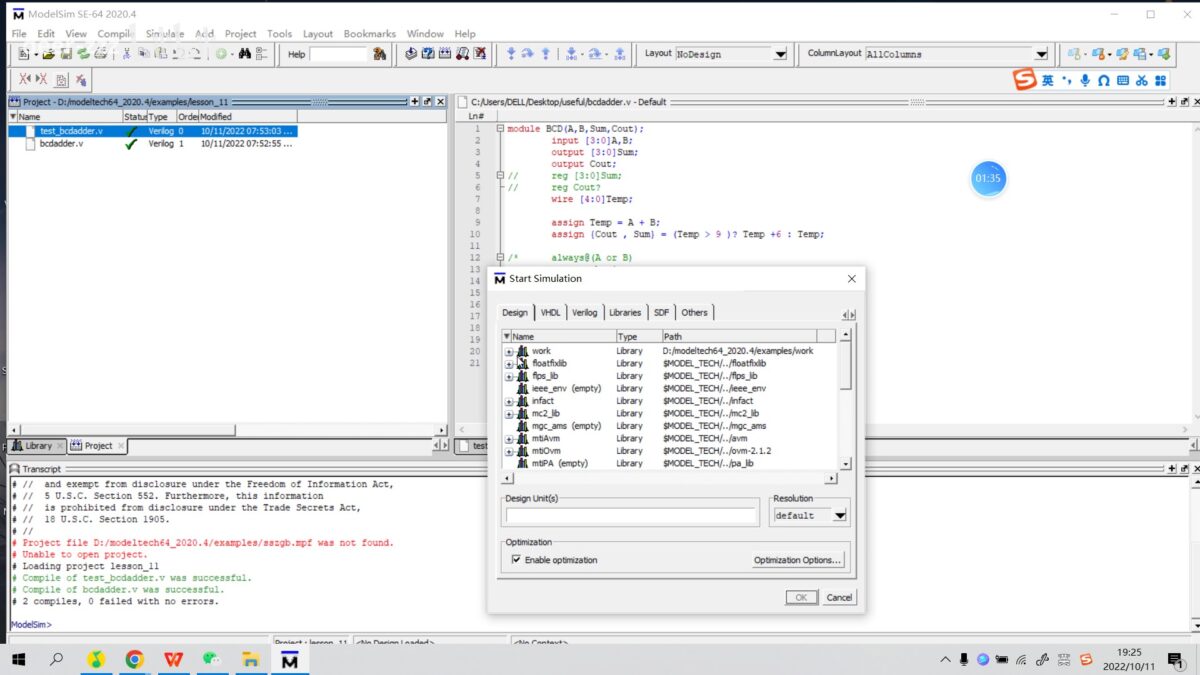

Synopsys VCS  ModelSim

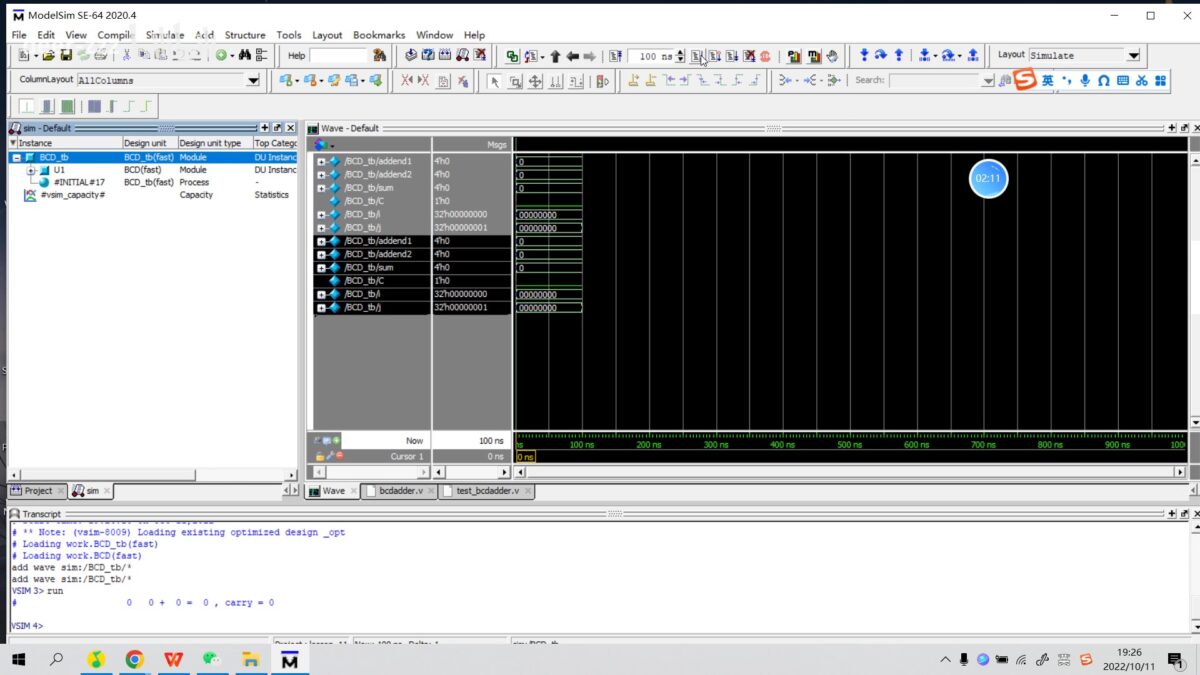

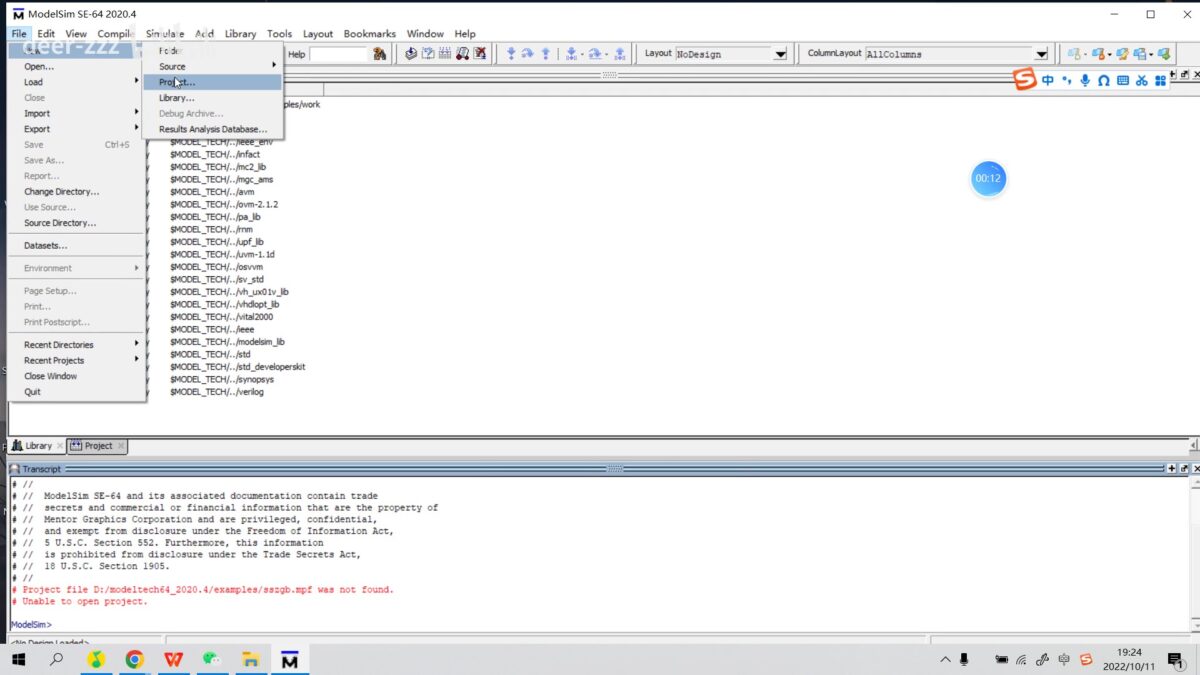

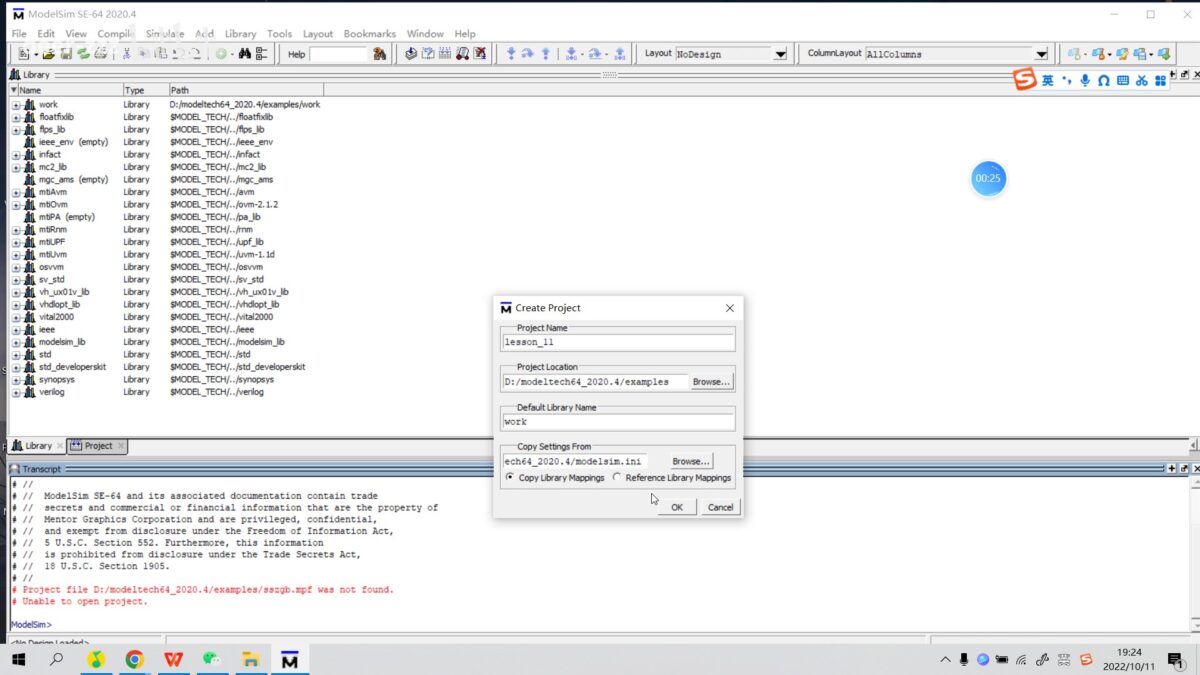

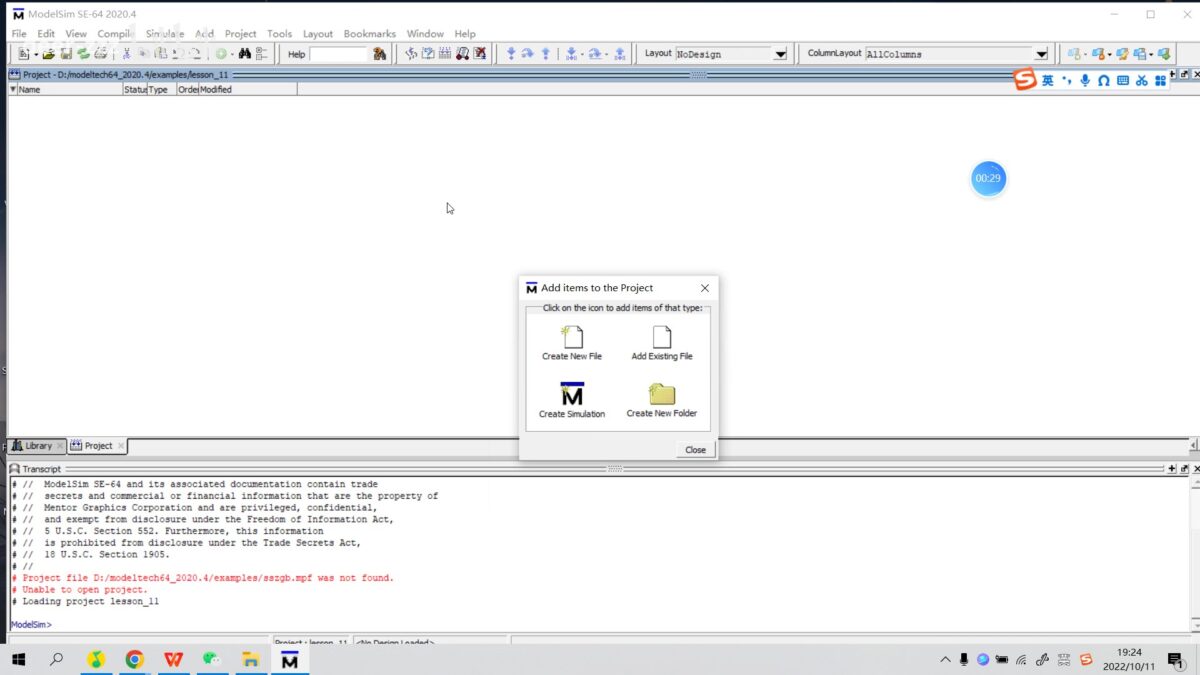

ModelSim

Cadence Xcelium Logic Simulation

Cadence Xcelium Logic Simulation  Robei EDA

Robei EDA

苏公网安备 32059002002276号

苏公网安备 32059002002276号