1. Cortex-A72处理器特性

Cortex-A72处理器是Armv8-A架构下的一款高性能、低功耗的处理器。它最多支持4个内核,内置L1和L2高速缓存。

Cortex-A72处理器具有以下特性:

采用Armv8体系结构规范来设计,ARMv8-A 架构配置文件的完整实现。

超标量处理器设计,支持乱序执行的流水线。

使用分支目标缓冲区(Branch Target Buffer,BTB)、全局历史缓冲区( Global History Buffer,GHB)、返回堆栈及间接预测器进行动态分支预测。

48项全关联L1指令转换后备缓冲区(Translation Lookaside Buffer,TLB),可以支持4KB/64KB及1MB大小的页面。

32项全关联L1数据转换后备缓冲区,可以支持4KB/64KB及1MB大小的页面。

每个处理器内核含有4路关联的1024项的L2转换后备缓冲区。

48K的L1指令缓存和32K的L1数据缓存。

可配置为512K/1M/2M/4M的L2共享缓存

基于AMBA4总线协议的高级可扩展接口的一致性扩展[AXI(Advanced eXtensible Interface) Coherency Extensions ,ACE]或一致性集线接口 (Coherent Hub Interface,CHI)

支持 PMUv3 架构的性能监控单元(Performance Monitor Unit,PMU)

支持多处理器调试的CTI(Cross Trigger Interface )

支持通用中断控制器GIC(Generic Interrupt Controller)

支持多电源域(power domain)的电源管理。

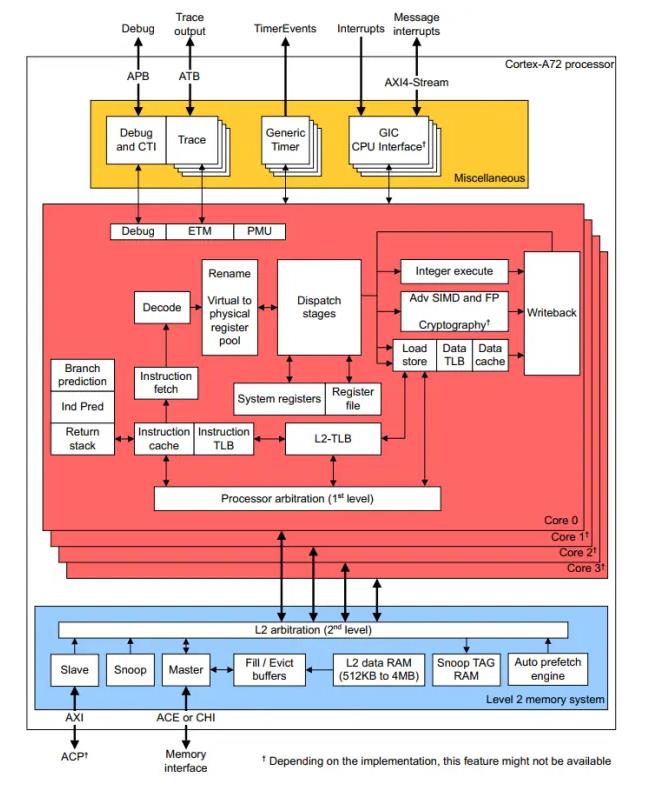

2. Cortex-A72处理器组成

框图:

2.1指令预取单元

指令预取单元从L1指令高速缓存中提取指令,并在每个周期将多达3个指令传送到指令解码单元。它支持动态和静态分支预测。

指令预取单元由如下部分组成:

L1指令高速缓存:48K3路关联高速缓存,64字节高速缓存双位奇偶校验。

48项全关联L1指令后备缓冲区(TLB)。

静态分支预测器

间接预测器

返回堆栈缓冲器

2.2指令译码单元

指令解码单元支持A32/T32/A64和高级SIMD及浮点指令集。指令解码单元还执行寄存器重名,通过消除写后写(WAW)和读后写(WAR)的冲突来实现乱序执行。

2.3指令分配单元

指令分配单元控制译码后的指令何时被分配到执行流水线以及返回的结果何时终止。

组成:

ARM核心通用寄存器

SIMD和浮点寄存器集

AArch32 CP15 和AArch64系统寄存器

2.4 加载/存储单元

加载/存储单元(LSU)执行加载和存储指令,包含L1数据存储系统,并为L2内存子系统的内存一致性请求提供服务。

组成:

32K两路组关联的L1高速缓存,缓存行为64字节。

支持32个全关联的数据后备缓存区(TLB)

自动硬件预取器,生成针对L1数据缓存和L1缓存的预取。

2.5 L1内存系统

L1内存系统保留指令内存系统和数据内存系统。

2.6 MMU

内存管理单元MMU用来实现虚拟地址到物理地址的转换。在AArch64状态下支持长描述符的页表格式,支持不同大小的页面。例如4KB/16KB/64KB。

2.7 L2 内存系统

L2内存系统不仅负责处理每个处理器内核的L1指令和数据缓存仲裁,还通过一致性扩展(ACE) 或 一致性集线接口(CHI)连接到内存系统。

苏公网安备 32059002002276号

苏公网安备 32059002002276号