10 点重要考虑

为什么芯片封装热协同设计如此重要?

芯片封装协同设计之所以重要,有以下几个原因。首先, 在一个大外形、大功率芯片(例如片上系统 (SoC))设计中,如果不考虑散热问题,则很可能在以后会出现问题, 导致其无论从成本、尺寸、重量还是性能方面来看,均不能称为理想的封装解决方案。其次,虽然在以往的 IC 设计中都已考虑到芯片温度要均匀,但是在许多情况下, 这已不再是一个有效的假设了。电流泄漏导致的发热(与温度相关)使功率耗散不均匀,加上使用更薄的芯片(现在已小于 50μm),更是降低了芯片自身的热扩散能力。这两种原因使得芯片上温度变化更大。

何时应该使用芯片封装热协同设计?

设计三维叠层集成电路 (3DIC) 等多晶粒芯片时,芯片封装协同设计就显得必不可少。由于芯片的电能和热能之间存在相互作用,因而不能独立地设计芯片。通过作为芯片间互连的硅过孔 (TSV)(虽然它们的主要作用是减少热点),有助于从芯片叠层中导出热量,因此,它们在芯片上相对于大功率区域的布局,会较大程度地影响整体热性能。热传递是高度的三维现象,因此,封装温度的分布会影响芯片上的温度分布。

热是阻碍三维设计成为半导体行业主流技术的关键挑战之一。其他问题包括缺乏完全支持三维设计的设计工具, 已知良好的芯片需要单独测试,以及更复杂的可测试性设计。还有热机械特性不同的材料叠层的组装问题,以及与更薄芯片相关的处理问题。尽管注重低功耗设计, 但大电流通过非常小的垂直连接让电力传输成为又一个颇具挑战性的方面。

本白皮书重点介绍三维芯片封装协同设计。三维封装中使用的先进技术意味着传统的芯片设计方法不能胜任, 例如:使用温度保护带来确保器件能在更大工作温度范围内工作,其中假设整个芯片的温度是均匀的。

随着三维 IC 功率密度的增加,封装级别的单位体积功耗也在提高。芯片叠层内产生的热量必须通过芯片叠层消除。芯片之间的键合提高了芯片间热阻,而芯片激进性地变薄以适应容许的封装高度降低了芯片散热的能力, 因此横向热阻也在增加。再加上三维电气连接和每个芯片上热源的非均匀分布,意味着传统的功耗感知 IC 设计流程不再胜任。IC 设计流程现在还需要完全的热感知能力, 并在整个 IC 设计流程中预测封装及其芯片的温度分布。

Simcenter 通过 Sahara/Simcenter Flotherm? 软件集成项目实现了完整的芯片—封装—系统热解决方案,提供从芯片级到系统级的精确设计建模的独特能力,例如在芯片内部、封装内部和对封装到系统进行建模。它支持导入非常精确的边界条件,以便为 IC 热分析提供更精确的芯片/封装建模。同样,精确的芯片/封装模型也可以向外传递到系统级别,进行精确的系统建模。为了理解这个主题,分三个阶段考虑 IC 设计流程会有帮助,尽管在实践中这些阶段可能有所重叠。

封装预选活动

第一阶段是封装选择,目的就是为相关 IC 选择更佳封装。

1. 始终先从封装选择开始

为了获得芯片内正确温度分布,有必要在热模型中加入这样一个封装结构 — 安装在典型的 PCB 上且适宜使用具有代表性的散热器解决方案,这样便可在预测整个封装的温度分布时考虑电路板上扩散的和进入散热器的热效应。要正确预测封装与其环境相互作用的方式并因此预测封装内正确的温度分布,需要此完整的计算流体动力学 (CFD) 仿真。

需要注意的是,简单地为芯片的每个表面施加一个恒定的热阻值以表示热流到环境的通道,不足以作为边界条件。与芯片本身近距离热接触的高热导率材料的存在, 使得到环境的高热阻不具有任何局部热扩散效应。这可能会保持芯片温度均匀而不显著贡献环境的总热阻。使用单一热阻值可能会导致设计过度且可能不正确。

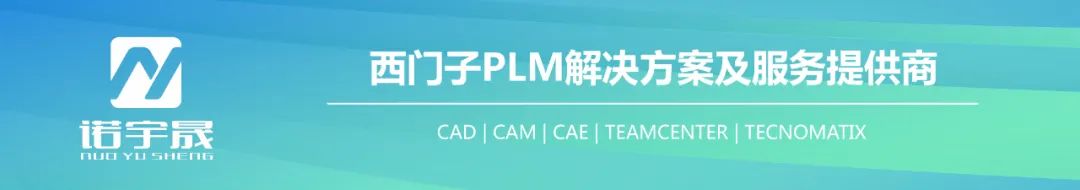

图 1:Simcenter Flotherm 中有多个芯片的 BGA 封装的详细热模型。

在前期设计中及在详细的 IC 设计工作开始前,优化芯片封装架构有更大的腾挪范围。在此阶段,对芯片数目的初步假设以及每个芯片的目标尺寸和功耗预算可用来创建候选封装的三维热传导模型(如果封装样式内部有空腔,还可以包括对流和辐射),而候选封装可用于探索封装设计空间。

2. 在 IC 设计开始之前,探索封装设计空间

候选封装的热模型可用于研究不同的芯片布局、封装尺寸和封装材料(例如球栅阵列 (BGA) 封装的基板中铜的量)对热性能的影响。

在这个阶段,自由度较高,因此有机会探究不同的封装选择和每一个设计。基于对芯片尺寸最初的估计,对于给定封装样式,可调查下列设计参数以确定它们对芯片温升和变化情况的影响:

● 硅过孔的数目和可能的 TSV Layout 影响

● 中介层的大小、形状和材料选择的影响

● 界面电阻的效果(胶接层)

● 金字塔结构与悬空叠层结构(如果引线键合)

● 封装内部的散热解决方案,如芯片边缘散热,内部散热片等

● 外部散热解决方案,例如焊盘、底部填充选项等的影响

特点是对芯片温升影响更大,变化情况说明需要进行更详细地建模和优化热性能。

3. 包括与温度相关的热特性

对于硅和列入 Simcenter Flotherm 材料库中的其他材料, 会自动包括与温度有关的热特性。整个芯片的温度范围可能会大到不能假设为单一的热导率值,所以必须有随温度变化的热导率才能精确地预测芯片热点值。请注意, 进行瞬态计算时,有必要加入材料密度和特定比热容。在 Simcenter Flotherm 中,当材料附加到对象时,会自动加入上述两项。

4. 完善芯片的表面处理

加入芯片活性层(金属和多晶硅)与几微米厚的各向同性块的三维表示。

通常用作介电材料分隔芯片活性表面上的金属引线的二氧化硅 (SiO2) 和硅酸盐玻璃,具有 1 W/mK 数量级的热导率,比其分隔的金属(传统上为铝或铜)大约低两个数量级。不同层次的引线走不同的方向,所以材料表现为局部各向异性。但是,应认识到不同层次的高电平互连, 加上不同方向上的金属走线,会引起热扩散。因此,对于主 IC 设计流程之外的前期设计活动,可将大部分行为近似看做各向同性材料,其带有在封装级别模型中一个网格单元厚度内捕获的所有活性表面层。

IC 工艺和设计技术文件中包含了有关金属宽度、间距以及优先布线方向的信息。这些信息可用于计算这个热活性层总厚度和平均的各向同性材料属性。

到这个阶段,热量应该在芯片中均匀地分布。但实际情况并非如此,还应进一步完善模型,以便一旦 IC 设计团队开始提供更详细的信息,就能立即消除这一假设。在开始时使用这一假设的好处在于,可给出芯片间温度从封装的有限能力上升到芯片整体保持均一温度的变化情况。

在 IC 设计工作开始之前有很多工作要做,但这种设计工作可能会占用很多人,因此良好的准备工作将确保这些资源得到尽可能高效地使用,而且 IC 设计的时间可以尽可能缩短。

前期设计芯片—封装热探索和优化

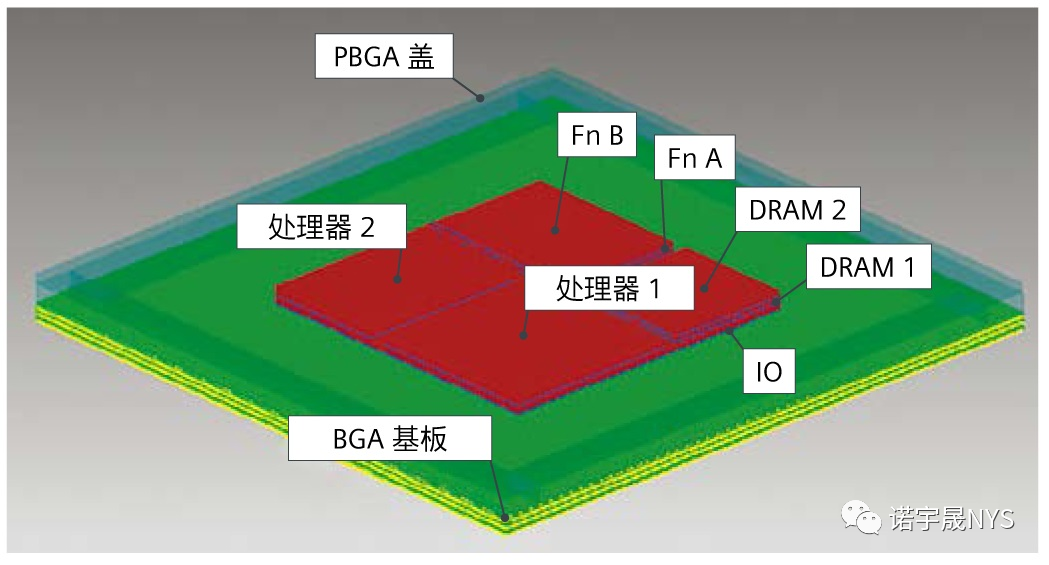

从热角度选择了最有效的封装,并理解了封装和芯片组合工作的热机制之后,便可开始封装—芯片的协同设计工作。此阶段的工作包括跨不同芯片的功能的三维分区、芯片的功能块和 TSV 布图规划以及接口层设计。因此, 我们处于图 2 所示过程的开端,但已经研究了候选封装类型的热性能:

图 2:封装-芯片热设计推荐流程。

5. 建立高效的工作流程

要进行封装级热仿真,需要从 IC 设计团队获得几何形状和功耗变化信息,并将其输入 Simcenter Flotherm。值得庆幸的是,Simcenter Flotherm 有 Simcenter Floscript 来记录软件中执行的操作,然后可以回放,从而无差错地重复相同的步骤。

这对于开发过程中必须反复进行的模型更改工作特别有用,例如:当前布图规划布局导致的每个芯片上的功率分布,以及穿过芯片以实现必要的芯片间电气连接的TSV 的数量和分布。

迅速更新模型的工作流程可以在封装预选阶段建立,以编程方式停用或删除原始几何形状,以及在重新求解某种情况之前加载和定位替换几何形状。

整合 Simcenter Flotherm 的 Calibre 温度感知设计流程

6. 在布图规划之前,反馈温度信息

在 IC 设计流程开始之前,为 IC 设计团队提供有关芯片平均温度和每个芯片温度变化的信息,可以极大地帮助进行布图规划 [参考文献 1]。布图规划对设计质量至关重要,因为在布图规划期间做出的决策可以缓解或加剧这种温度变化。就像封装预选活动一样,前期 IC 设计旨在探索设计空间,以便提出将热影响考虑在内的更佳解决方案,因此必须快速评估许多想法。

现在可以快速迭代不同布图规划的热影响,这些布图规划同时将封装的热设计直接整合到 IC 设计流程中,因为Simcenter Flotherm 现在可以与 Simcenter 的 Calibre 套件(DESIGNrev 和 RVE)一起用来仿真 Calibre 内置封装的热模型,提供具有完全温度感知能力的 IC 设计流程, 其代号为 Sahara 项目。

Sahara 项目专注于从前期设计探索到最终 sign-off 的全流程。Sahara 项目可以创建 3DIC 的 Simcenter Flotherm 模型,使得 3DIC 封装能够导入到更大的电路板级或系统级模型中,从而充分考虑应用环境的影响。

7. 在布图规划期间使用功能块功率预算

一旦开始进行布图规划,您需要从 IC 设计团队处拿到高层次的功率映射,导入到封装的热模型中。

Simcenter Flotherm 拥有的 Die SmartPart 可以读入 CSV 文件格式的功率,从而自动完成并迅速反馈结果,因为仿真模型往往只需要运行短短的几分钟,就可指明 TSV 在哪里引入可改善散热性能或哪里需要其他设计变更。例如,对于确保两个或更多个不同功能块在非常相似的温度下运行以消除定时问题,它可能会非常重要。

8. 探索硅通孔布局

对于逻辑搭载逻辑的 3DIC,这应该在不同芯片之间隔开设计时,和在芯片间和芯片内布图规划期间(要求每个芯片的功率映射)加以考虑。

在此阶段,有机会在保持功能块相对位置不变的情况下, 将其沿 x 和 y 方向(xy 扩展)移动,只是调整它们之间的间距(空白空间)使得能够插入 TSV 以检查它们对芯片热点的影响。在知道与芯片厚度成比例关系的 TSV 尺寸和间距后,具有更高的贯通面热导率的块可以叠加到Simcenter Flotherm 中的这些空白区域的芯片厚度上, 以局部覆盖硅的属性。

在布图规划期间优化功能块和 TSV 布局将是 IC 设计流程的一部分,而热设计只是该过程的约束条件之一。

9. 使 IC 设计流程感知温度

随着布图规划的推进,在进一步细化设计时,热设计工作需要把重点放在芯片之间的热相互作用的细节上。芯片的功率映射变得更加详细,并且在 3DIC 的情况下,作为电气设计的一部分,需要定义 TSV 的数量和位置。时钟树综合 (CTS) 是 IC 设计流程中的关键步骤,必须等到它完成后,芯片才能布线;物理时序收敛要考虑布局、时钟树综合和布线,这些都必须具有时序感知能力才能让现代同步 IC 设计实现时序收敛。

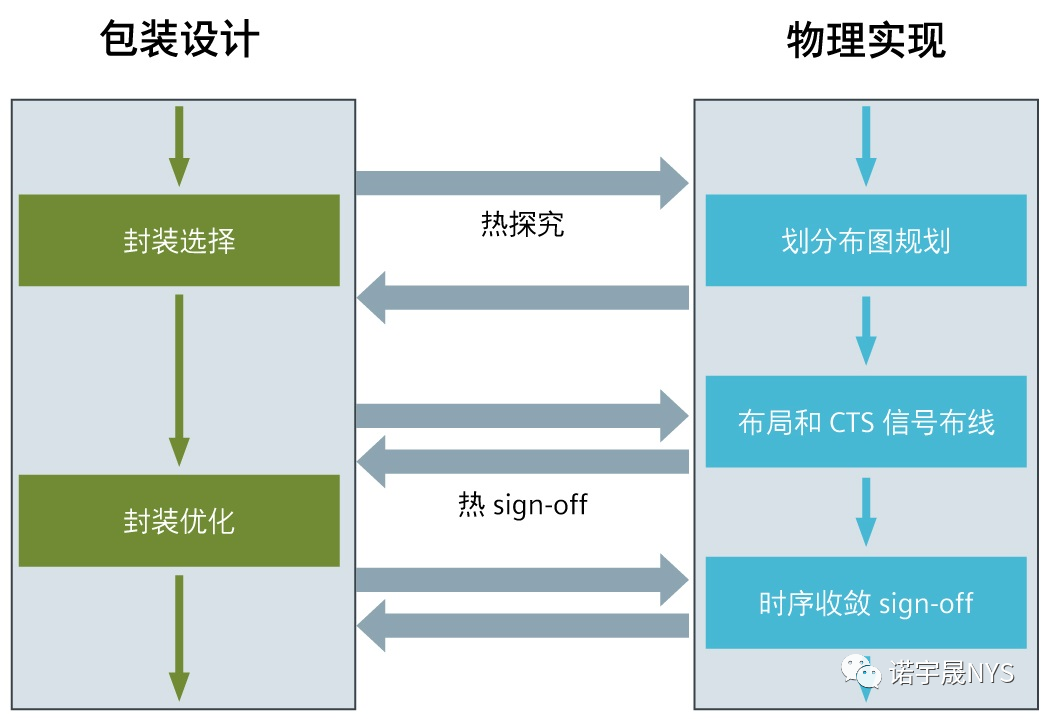

Siemens 公司与 TSMC 携手创建基于 Simcenter FloTHERM 和 Calibre DESIGNrev 与 RVE 的热分析流程,是一个观察环境的工业标准的物理验证结果 [参考文献 3]。

图 3:TSMC 参考流程协作。

Sahara 项目对于获得时序收敛和 sign-off 同时有热感知能力的设计所需的精细具体工作至关重要。它提供了简单易用、快速准确的工具,通过内置于该解决方案的自动网格化功能,在关键的模型区域(如芯片)使用局域化网格的方式实现对完整封装模型内 3DIC 的芯片和中介层的热仿真。

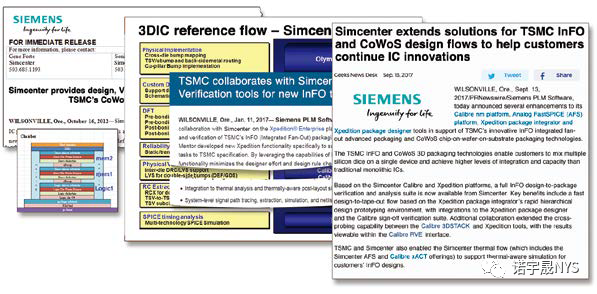

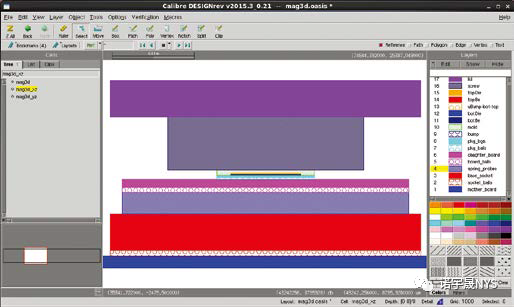

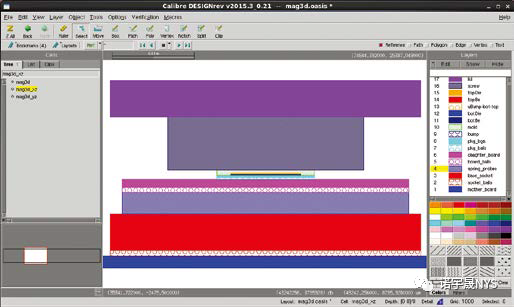

图 4:Caliber DESIGNrev 中的热模型的装配视图。

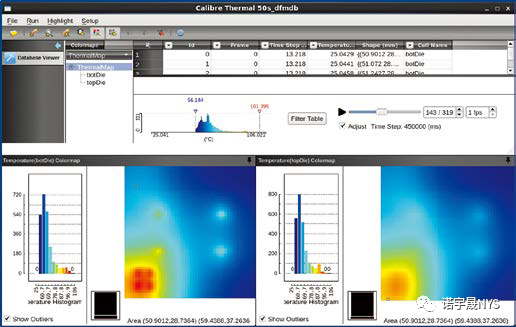

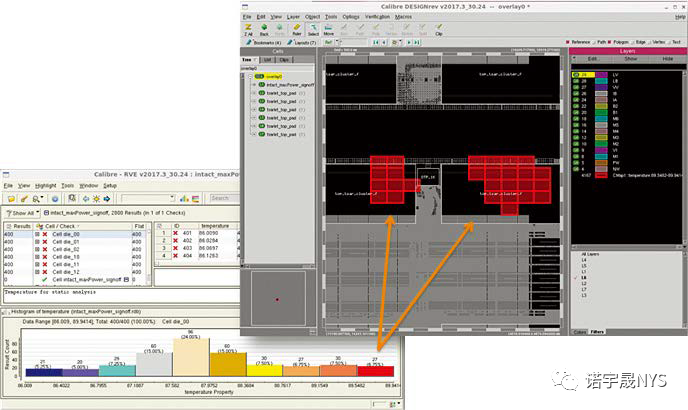

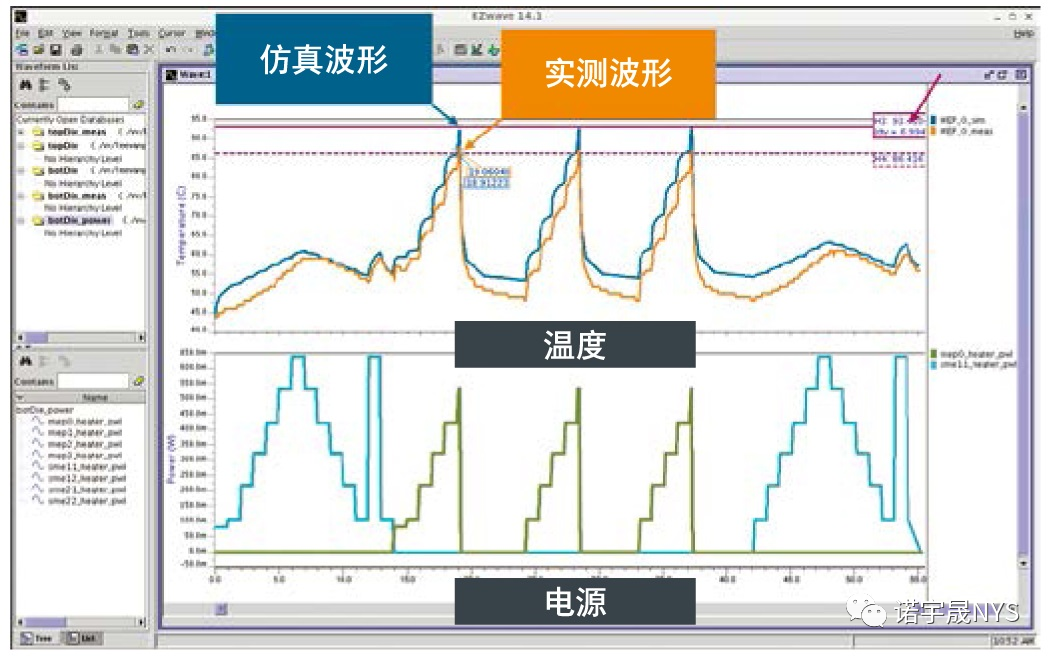

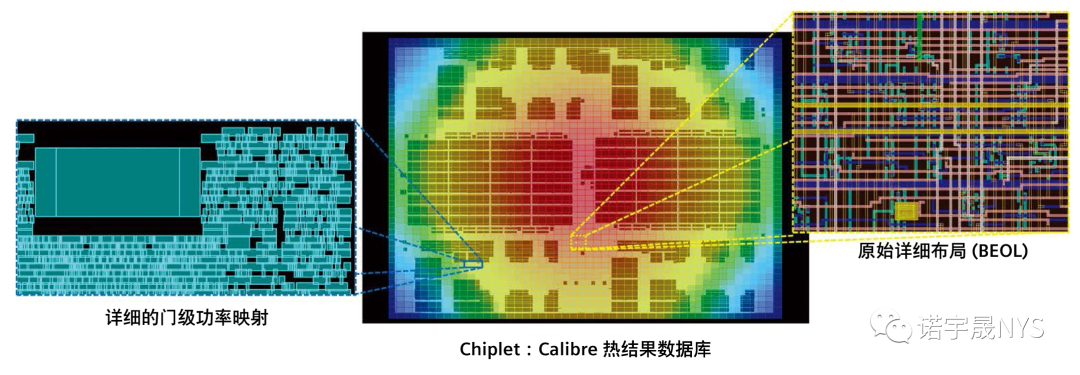

此解决方案利用能够由功率分析工具生成的芯片功率映射文件创建热量分布图,以用于散热设计和进行散热的约束违规检查。热结果还可以在 Calibre RVE 中以直方图形式显示,并且在 Calibre DESIGNrev 中,热点会在设计中突出显示。在瞬态分析中,可以使用高容量、高性能的图形化波形环境 Simcenter EZwave 显示温度与时间的关系图。功率和温度波形可以显示在同一窗口上,甚至可以叠加以便轻松获得相关性。

图 5:Sahara 项目的热建模方法。

在此流程中,热模型的生成和验证,基于 GDSII 的热特性提取,以及基于实例功率文件 (IPF) 的功率映射生成, 均是在 Calibre 环境中完成。因此,考虑到金属化,例如互连和芯片内的 TSV,芯片的热模型比在 IC 设计流程之外通常能构建的模型更精确。

图 6:Sahara 项目中的热彩色图和直方图。

图 7:Calibre RVE 中的热直方图和 Calibre DESIGNrev 中的热点覆盖。

图 8:利用 Simcenter EZwave 显示的温度和功率与时间的关系曲线。

时序收敛和 sign-off

10.使用精确的芯片级热分析

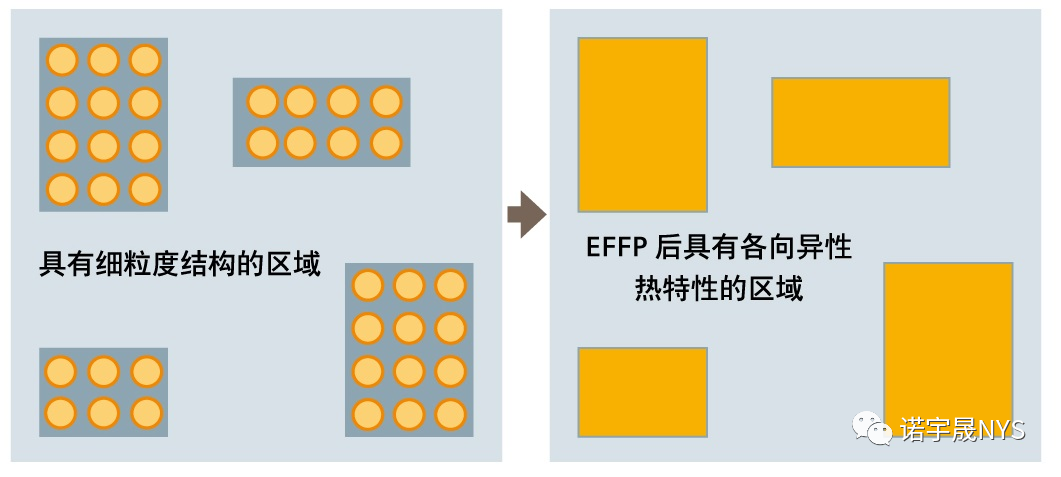

当执行完整的芯片—封装—系统热仿真时,通过从布局中提取来自动计算各向异性等效热特性,可以解决细粒度细节问题。随着重心转向获得时序收敛和 signoff,提取的粒度可以增加。

图 9:高效热特性提取 (EFFP) 可降低模型复杂度并加速仿真(图片由 CEA-Leti 提供)。

IPF 支持允许使用门级和器件级功率分析来构建所需的细粒度功率图,以便精确捕获芯片上的热点。在实例数量非常多(源实例达数百万)的设计中自动压缩电源,可以加速 Simcenter Flotherm 仿真。

图 10 显示了使用 EFFP 和有 9 个金属化层的非常复杂的BEOL 简化之后,一个拥有超过 150,000 个细粒度结构

(包括 TSV 和 μ-凸块)的器件可能达到的细节水平。

最后,自动约束检查可以避免容易出错且耗时的热约束手动验证。对于图 10 所示设计,EFFP 和智能功率映射转换功能将仿真时间从数小时/数天缩短到不到一小时:

● 热特性提取 (EFFP):30 分钟(每个热模型一次)

● 从 IPF 生成功率映射:不到 2 分钟(每个应用场景一次)

● 完整封装三维 IC 的热仿真:50 分钟

图 10:详细的 sign-off 热分析(图片由 CEA-Leti 提供)。

结语

在先进技术和现代应用中,主要是高级三维 IC 中, 以封装为中心的方法不再有效。集成 Sahara 项目的Simcenter Flotherm 是一个功能强大且灵活的平台,支持如下功能:

● 兼容高级三维集成技术的详细芯片级热建模

● 带有真实边界条件的完整芯片—封装——系统热仿真

● 易于与标准 ASIC 设计流程集成

● 利用 EFFP 功能对非常复杂的设计进行精确建模

● 热感知三维分区和前期封装协同设计

● 复杂多芯片设计的 sign-off 热分析

● 跨芯片—封装设计流程的快速、详细、精确的热评估

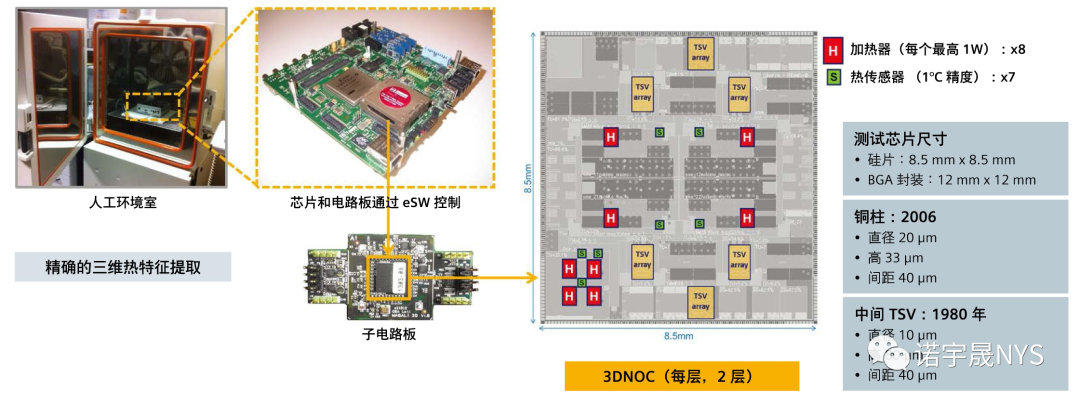

CEA-Leti [参考文献 4、5] 描述了将集成 Sahara 项目的Simcenter Flotherm 用于 4G 电信应用的异构逻辑搭载逻辑三维片上网络异步多核器件,包括 DFT 和容错设计。

“ 所实现的热模型具有很高的精度,最坏情况下仿真数据和测量数据之差等于 3.75%,而考虑所有热传感器的平均差异低于 2%。”

图 11:3DNOC – 热特征提取测试的实验设置(图片由 CEA-Leti 提供)。

苏公网安备 32059002002276号

苏公网安备 32059002002276号